Moderne Test- und Regelsysteme werden nicht nur zunehmend komplexer, sondern auch stetig komplizierter in der Umsetzung. Entwickler stehen häufig vor der Aufgabe, große Datenmengen sowohl mit immer höherer Geschwindigkeit und steigender Kanalanzahl erfassen und erzeugen, als auch mit minimaler Latenz übertragen und direkt verteilt verarbeiten zu können. Neben diesen Anforderungen müssen sich Test- und Regelsysteme durch weitere Eigenschaften wie Flexibilität, Skalierbarkeit, Modularität, niedrige Gesamtsystemkosten und Vendor-Interoperabilität auszeichnen. Der PXI-Multicomputing(PXImc)-Standard, der durch die PXI Systems Alliance (PXISA) im November 2009 verabschiedet wurde, versucht diesen Anforderungen mit kommerziell verfügbaren Technologien (COTS) gerecht zu werden.

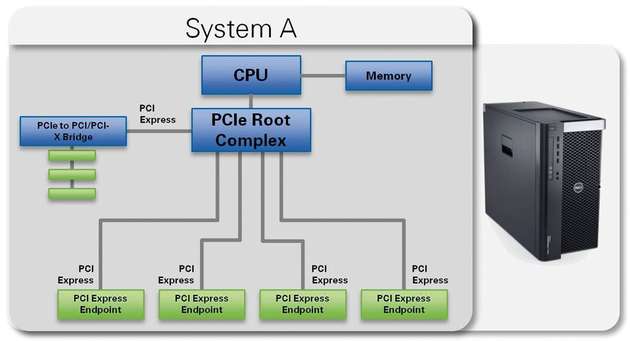

Er definiert die Hardware- und Softwareanforderungen, um zwei oder mehrere „intelligente“ Systeme über PCI(Peripheral Component Interconnect)- oder PCI-Express-basierte Schnittstellen und eine so genannte nicht-transparente PCIe-Brücke (NTB) miteinander zu verbinden. Der PCIe-Bus bietet einen hohen Datendurchsatz mit mehreren GBit/s und eine geringe Latenz im Bereich von µs und ist somit gut geeignet, diesen Anforderungen mit einem optimalen Kosten-Nutzen-Verhältnis gerecht zu werden. Die typische Struktur eines PCI-Express-basierten Host-Systems kommuniziert über den Systembus und PCIe-Switches (Root Complex) mit den PCI/PCIe-Geräten (Endpoint Devices) und dient als Schnittstelle zum zentralen Verarbeitungssystem. Das Verarbeitungssystem stellt eine Verbindung zum Systembus her, um allen PCI/PCIe-Geräten des Systems die erforderlichen Ressourcen – Bus, RAM, CPU, und so weiter – zugänglich zu machen.

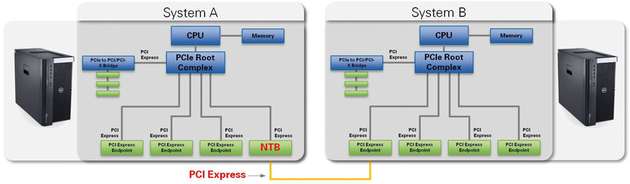

Der PXImc-Standard spezifiziert ein Kommunikationsmodell in dem PCI/PCI-Express als physikalische Kommunikationsschicht eingesetzt wird und damit einen hohen Datendurchsatz mit mehreren GBit/s und eine Latenz im Bereich von wenigen µs realisiert. Eine direkte Verbindung zwischen zwei Systemen mit eigenen Systembussen kann jedoch nicht direkt über PCI/PCI-Express erfolgen, da dies unweigerlich zu Ressourcenkonflikten zwischen den beiden eigenständigen Bereichen, den PCIe-Domains, führen würde – beispielsweise bei der Busverwaltung und Endpunkt-Ressourcenvergabe. Die Verwendung einer NTB löst diese Problematik, indem die PCI-Bereiche logisch voneinander getrennt werden, gleichzeitig aber ein Mechanismus bereitgestellt wird, mit dem bestimmte Daten von einem PCIe-Bereich auf den anderen übertragen werden kann – Inter-Domain Switching.

Systembandbreite und -performance

Da PXImc-PCI-Express als physikalische Kommunikationsschicht verwendet wird, hängt die Leistung einer PXImc-Verbindung vom Typ der PCI-Express-Schnittstelle ab. Im Vergleich zu klassischem Gigabit-Ethernet stellt die PXImc-Verbindung in etwa eine 10-mal höhere Bandbreite und 100-mal geringere Latenz dar und validiert den PXImc-Standard als Schnittstelle für den Aufbau von High-Performance-Mehrrechnersystemen in modernen Test- und Regelanwendungen. Zukünftige Verbesserungen am PCI-Express-Standard können so automatisch die Leistung von PXImc weiter skalieren.

Anwendungen

Die folgenden drei Anwendungsbereiche profitieren am meisten von der PXImc-Technologie:

Hybride, High-Performance Mess-und Prüfsysteme

Mehrere Systeme mit (Multicore-)CPUs für die verteilte Verarbeitung (Distributed-Chassis Multi-Master Processing)

Einzelsysteme mit von x86-basierten CPUs als Co-Prozessoren (In-Chassis Multi-Master Processing)

Komplexe Mess- und Prüfsysteme wie sie zum Beispiel im Bereich HIL (Hardware in the Loop) zu finden sind, bestehen typischerweise aus verschiedenen diskreten Teilsystemen (Subsystem, Secondary Nodes), die unterschiedliche Funktionen erfüllen. Oft sind diese Teilsysteme sogar auf unterschiedlichen hybriden Hardware-Plattformen und Zielgeräten realisiert, die von der Verarbeitungsleistung und -geschwindigkeit optimal sind und den funktionalen Anforderungen des Gesamtsystems am einfachsten gerecht werden. Die PXImc-Spezifikation ermöglicht die Verbindung dieser Teilsysteme über eine PCIe-Verbindung und bietet die ideale Kombination aus Leistung, Flexibilität und Kosteneffizienz. Durch die Nutzung von PXImc als Kommunikationsbus können solche Systeme im Vergleich zu Gigabit-Ethernet-Netzwerken und der Reflective-Memory-Technologie kürzere Test- und Zykluszeiten realisieren und so, zum Beispiel im Falle von HIL-Anwendungen, genauer reale Bedingungen nachbilden.

Anwendungen aus den Bereichen Signal Intelligence (SIGINT) und Real Time High Performance Computing (RTHPC), die Echtzeit- oder/und Inline-Datenverarbeitung erfordern, brauchen in der Regel leitungsstarke Datenverarbeitungsfähigkeiten, um mit dem kontinuierlichen Datenstrom Schritt halten zu können. Diese Anwendungen müssen die Fähigkeit haben, die Verarbeitungslast zwischen mehreren diskreten Verarbeitungsknoten (Nodes) mit einer Kommunikationsschnittstelle, die eine hohe Bandbreite und niedrige Latenz bietet, zu verteilen.

Bei einigen verteilten Verarbeitungssystemen, kann die Verwendung von Field-Programmable Gate Arrays (FPGAs) und diskreten digitalen Signalprozessoren (DSPs) als Co-Prozessoren diesen Bedarf unter Umständen decken.Manche Anwendungen erfordern jedoch den Einsatz von bestehender x86-basierter Software-IP oder müssen Floating-Point Operationen direkt durchführen können. In solchen Fällen bietet die PXImc-Technologie die Möglichkeit, mehrere verteilte Verarbeitungssysteme (x86 Compute Node), die die neuesten Multicore-CPU-Technologie verwenden, als zusätzliche externe

Rechenknoten zu verwenden.

Die PXImc-Spezifikation ermöglicht in der dritten Variante, dass die Rechenknoten direkt On-Board NTBs einsetzen. Dies bedeutet, dass sich solche Prozessormodule in einem Peripherie-Slot eines PXI-Express-Chassis befinden können und direkt die Chassis-Backplane verwenden um mit den PXI-Modulen (Endpoints) und/oder dem PXI-Controller (Master) zu kommunizieren. Mit dieser peripheren In-Chassis-Verarbeitung erhöht sich die gesamte Verarbeitungskapazität von einem einzigen System und bietet eine kompakte und robuste Lösung. Diese Variante ist für die Verarbeitung von rechenintensiven Test- und Regelaufgaben, minimiert die Gesamtsystemgröße und vereinfacht die Portabilität von System zu System. Die PXImc-Spezifikation ermöglicht auch direkte Kommunikation (Peer-To-Peer, P2P) zwischen PXI-Modulen (Messgeräte) und anderen PXImc-PCI-Express-Karten. Diese Funktion kann insbesondere dazu verwendet werden, um Subsysteme innerhalb eines einzigen PXI-Chassis zu erstellen und somit die Chassis-Ressourcen effizienter zu nutzen.

Schnittstellenmodul

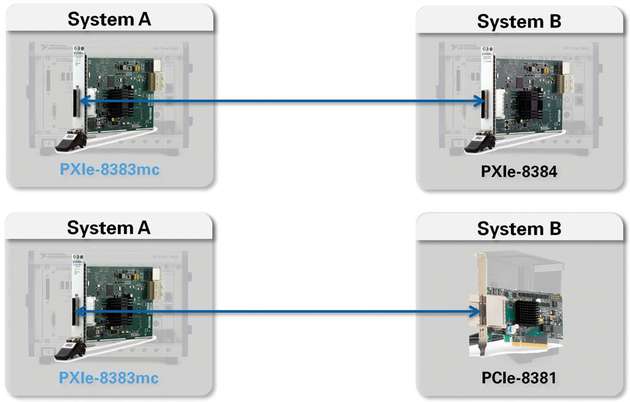

Das Modul NI PXIe-8383mc ist das industrieweit erste PXImc-Schnittstellenmodul von NI. Diese Hardware kann mit LabVIEW (32/64-Bit), C und C++ über den PXImc-1.0-Treiber integriert werden und ist unter Windows 7 und LabVIEW Real Time (LabVIEW RT) einsetzbar. Es verwendet ein PCIe-Kabel (PCIe-x8-Verbindung) zu unterschiedlichen Host-Adaptern – entweder ein PXIe-8384 Modul, um weitere, sekundäre PXIe-Systeme anzubinden oder eine PCIe-8381 Karte, um sich mit PC-basierten Rechenknoten zu verbinden. In dieser Konfiguration lässt sich ein Datendurchsatz von bis zu 3 GBit/s bei einer Latenz von 4 µs erzielen. Es wird empfohlen ein 64-Bit Win7 OS zu verwenden und das System mit mindestens

8 GByte RAM auszustatten, um die maximale Streaming-Leistung zu erzielen.

Pro PXI-System können nicht nur mehrere PXImc-Module eingesetzt werden, denen jeweils eigenständige Betriebssystem-/Systemressourcen zugewiesen werden, sondern es besteht auch die Möglichkeit mehrere Sessions pro PXImc-Modul zu erzeugen. In diesem Fall wird der durch den Treiber allokierte Speicher zwischen den Sessions aufgeteilt und jede Session ist über eine eigene ID eindeutig identifizierbar. Der Vorteil von mehreren, parallelen Sessions liegt zum Beispiel in der logischen Trennung von Daten und Steuerbefehlen. Die Verbindung von zwei PCIe-Bereichen (Domains) zum Datenaustausch über NTBs, lässt sich über die PXImc-API in NI LabVIEW bewerkstelligen. Dazu werden zwei Prozesse auf den unterschiedlichen Systemen erzeugt, die kontinuierlich Daten austauschen und über die zuvor genannte Connection-ID identifiziert sind.

Den Anforderungen gerecht werden

Entwickler von Test- und Regelsysteme müssen häufig große Datenmengen mit immer höherer Geschwindigkeit und steigender Kanalanzahl erfassen und erzeugen, diese mit minimaler Latenz übertragen und direkt verteilen. Der PXI-Multicomputing(PXImc)-Standard, versucht diesen Anforderungen mit kommerziell verfügbaren Technologien (COTS) gerecht zu werden. Er definiert Hardware- und Softwareanforderungen, um zwei oder mehrere Systeme miteinander über PCI-Express-basierte Schnittstellen und eine nicht-transparente PCIe-Brücke (NTB) zu verbinden. Diese Vorgehensweise ist für einen hohen Datendurchsatz mit mehreren GBit/s und eine geringe Latenz im Bereich von µs geeignet.

Weiterführende Literatur

[1] PXI-7 PXI MultiComputing Hardware Specification, Rev. 1.0, PXI System Alliance, September 2009

[2] PXImc - Overview, Configurations & Tips, NI Whitepaper, C. Kapoor, National Instruments Corp., July 2013