Obwohl grundsätzlich viele Variationen möglich sind, wird im Folgenden davon ausgegangen, dass eine Eingangsspannung (Vin) von -12 V verfügbar ist, aus der eine Ausgangsspannung (Vout) von -3,3 V erzeugt werden soll. Für diese Umwandlung wird ein Boost-Wandler-IC eingesetzt – jedoch in einer Buck-Topologie. Diese eignet sich zur Spannungswandlung in Anwendungen, in denen |Vout| < |Vin|. Das gewählte Boost-Wandler-IC vom Typ TPS61170 mit integriertem MOSFET arbeitet mit einer Schaltfrequenz (Fsw) von 1,2 MHz und bietet mit seinem nur 2 x 2 mm großen QFN-Gehäuse die nötigen Voraussetzungen für eine stark miniaturisierte Lösung. Auf die Verwendung anderer ICs für Anwendungen mit höherer Leistung wird hier ebenfalls eingegangen.

Feedback-Pegelumsetzer

Im beschriebenen Beispiel ist die Ausgangsspannung auf 0 V bezogen. Allerdings ist zu beachten, dass der GND-Pin des IC mit -Vin verbunden ist. Deswegen wird ein Pegelumsetzer benötigt, um die Ausgangsspannung in einen für den Feedback-Pin des IC geeigneten Pegel umzusetzen. Diese Schaltung ist im Beispiel ein PNP-Transistorpaar. Im statischen Zustand und nach den kirchhoffschen Regeln für die Schleife aus den Basis-Emitter-Spannungen und dem 3,3-kΩ-Widerstand ergibt sich, dass an dem 3,3-kΩ-Widerstand die Ausgangsspannung (Vout) liegt. Das verursacht einen Stromfluss von 1 mA, da sich die Basis-Emitter-Spannungen beinahe aufheben.

Ein Strom von 1 mA fließt auch durch den 1,23-kΩ-Widerstand, an dem somit 1,23 V abfallen. Diese Spannung ist gleich der Regelungsspannung des IC (FB = Vref = 1,23 V). Der Widerstandswert von 10 kΩ wurde so gewählt, dass durch den Transistor T2 ein Strom von rund 1 mA fließt. Die beiden PNP-Transistoren sind vom Typ PMP5201Y, doch können ebenso gut auch andere Typen eingesetzt werden. Das simulierte Bode-Diagramm bescheinigt dem Pegel-

umsetzer bis mindestens 400 kHz einen nahezu flachen Phasengang, bevor sich langsam ein Phasenverzug im System einzustellen beginnt.

Eine andere Pegelumsetzer-Implementierung besteht aus einem Operationsverstärker und einem MOSFET, die gemeinsam eine Stromquelle bilden. Die Ausgangsspannung Vout (-3,3 V) am 3,3-kΩ-Widerstand erzeugt einen Strom von 1 mA, was im geregelten Zustand einen Spannungsabfall von 1,23 V am 1,23-kΩ-Widerstand bewirkt. Der Operationsverstärker lässt sich mit 0 V und -Vin speisen. Da die Gleichtakt-Eingangsspannung am Operationsverstärker Werte bis 0 V (also bis zur positiven Versorgungsspannung) erreichen kann, muss der Gleichtaktbereich des Operationsverstärkers dies zulassen. Geeignet ist ein Operationsverstärker mit Rail-to-Rail-Eingang wie der LM7341. Steht im System alternativ eine positive Spannung (+Vcc ≥ 2,5 V) zur Verfügung, lässt sich der Operationsverstärker auch mit +Vcc und -Vin speisen. In diesem Fall kommt ein Operationsverstärker wie der OPA172 infrage, der keinen wirklichen Rail-to-Rail-Eingangsspannungsbereich bietet.

Kompensation der Regelschleife

Obwohl ein Boost-Wandler-IC verwendet wird, handelt es sich bei der Wandlertopologie, die hier eine negative Eingangsspannung in eine negative Ausgangsspannung umwandelt, um einen Abwärtswandler, sodass die entsprechenden Regelgesetze zum Tragen kommen. Über die Peak-Current-Mode-Kompensation wurde bereits viel geschrieben; im vorliegenden Fall wird eine einfache Lösung gewählt, wie man sie unter anderem in den Datenblättern von Buck-Wandler-ICs wie dem TPS54388-Q1 findet. Dieses Konzept kommt in Betracht, solange die gewünschte Durchtrittsfrequenz nicht zu hoch angesetzt wird. Oberhalb dieser Marke nämlich beginnt das einfache Modell zu versagen, sodass ein ausgefeilteres Modell benötigt wird, um den Amplituden- und Phasengang exakt vorherzusagen. Im Fall des TPS61170 wurde eine Durchtrittsfrequenz von Fc = 1,2 MHz / 50 = 24 kHz gewählt. Der Cout-Wert von 22 μF wurde auf 20 reduziert, um die Auswirkungen der DC-Vorspannung zu berücksichtigen. (siehe Formel 1)

Darin handelt es sich bei Rcomp und Ccomp um die Kompensations-Bauelemente, Gm(ea) ist die Transkonduktanz des Fehlerverstärkers, Gm(ps) ist die Transkonduktanz der Leistungsstufe (1 / Rsense), Cout ist die Kapazität des Ausgangskondensators, Rload ist der Lastwiderstand (Vout dividiert durch den maximalen Laststrom), und bei Vref handelt es sich um die Referenzspannung des IC, die auch am FB-Pin liegt. Ein Kondensator zur Kompensation einer hochfrequenten Nullstelle des Fehlerverstärkers wurde weggelassen, da die Kombination von Cout und seines ESR bei einer sehr hohen Frequenz liegt.

Die gewählten Kompensations-Bauelemente ergeben eine Polstelle Fp(ea) und eine Nullstelle Fz(ea) bei den ungefähren Frequenzen von 0,6 Hz und 1,4 kHz (siehe Formel 2), wobei Rea der Ausgangswiderstand des Fehlerverstärkers ist. Wie zu erwarten, liegt Fp(ea) bei einer sehr niedrigen Frequenz. Die Berechnung der Verstärkung Gz(ea) bei der Frequenz Fz(ea) erfolgt nach Formel 3.

Die dominante Polstelle F(ps) der Leistungsstufe und deren DC-Verstärkung G(ps) werden nach Formel 4 berechnet.

Simulation mit TINA-TI

In dem gewählten Beispiel ist der GND-Pin des IC mit -Vin verbunden. Dies kann ein Problem für die Simulation der Schaltung sein, da IC-Simulationsmodelle für Bauelemente wie den TPS61170 oft unter der Annahme geschrieben werden, dass der GND-Pin des IC-Modells mit dem Schaltungsknoten 0 verbunden ist und alle internen Schaltungen des Modells direkt mit Knoten 0 statt mit dem GND-Pin des IC verbunden sind. Deswegen darf nur der GND-Pin des IC-Modells mit gnd (Knoten 0) verbunden werden. Um dieses Problem zu umschiffen, werden alle auf 0 V (gnd) und -Vin liegenden Knoten in der tatsächlichen Schaltung von Bild 1 um +Vin pegelverschoben. Der ursprünglich auf -Vin befindliche GND-Pin des IC liegt so auf 0 V, und die sonst auf 0 V liegenden gnd-Knoten liegen auf +Vin. Diese Pegelumsetzung ermöglicht einen ordnungsgemäßen Ablauf der Simulation, hat aber keine Konsequenzen für die Simulationsergebnisse der Schaltung.

Die Resultate der Simulation zeigen, dass sich Vout nach 7,25 ms auf -3,37 V stabilisiert. Bei 7,5 ms wird eine zusätzliche Last zugeschaltet (indem der Laststrom effektiv von 300 mA auf 600 mA verdoppelt wird), und bei 8,5 ms wird diese zusätzliche Last wieder entfernt. Die Regelgenauigkeit von Vout während dieser Lastsprünge beträgt ±90 mV. Die Schaltungen mit den beiden verschiedenen Pegelumsetzern schnitten bei diesem Test übrigens gleich ab.

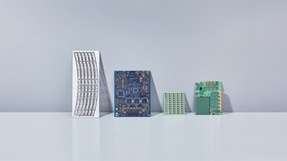

Getestet wurden die Schaltungen aus den Bildern 1a und 1b. Der Eingangskondensator Cin in Bild 1 sollte direkt zwischen dem GND-Pin des IC und der Katode der Freilaufdiode platziert werden, und die Pegelumsetzer-Schaltung für die Rückkopplung wird am besten nahe dem FB-Pin des IC angeordnet. Die Abtastung von Vout sollte über Leiterbahnen erfolgen, die in geringem Abstand parallel verlaufen und direkt zu den Pads von Cout führen. Die Schaltung in Bild 1b erfordert einen lokalen Entkopplungs-Kondensator von 100 nF für den Operationsverstärker. Bei beiden Schaltungsvarianten benötigte der monoton und ohne Überschwinger erfolgende Anlaufvorgang des Wandlers 6 ms. Eine resistive Last von

11 Ω bewirkte einen Laststrom von 300 mA, und zum Testen des Lastsprungverhaltens wurde zeitweilig ein weiterer 11-Ω-Widerstand parallelgeschaltet, um den Laststrom auf 600 mA anzuheben. Die Ergebnisse des Lastsprung-Tests für die Schaltung aus Bild 1a lassen eine Regelgenauigkeit von ±100 mV bei -3,34 V erkennen. Die entsprechenden Ergebnisse für Bild 1b sind mit ±100 mV bei -3,39 V nahezu identisch.

Leistungsstärkere Designs

Ein höherer Ausgangsstrom von mehreren Ampere lässt sich mit dem TPS61175 realisieren, ein noch höherer Strom mit dem TPS55330. Sollen Spannung und Strom angehoben werden, empfiehlt sich der TPS55340. Diese drei Bausteine arbeiten ähnlich wie der TPS61170, jedoch besitzen TPS61175, TPS55330 und TPS55340 zusätzliche Features wie eine einstellbare Schaltfrequenz, die Möglichkeit der Synchronisation der Schaltfrequenz zu einem externen Takt sowie eine einstellbare Softstart-Funktion.

Die Schaltpläne für die leistungsstärkeren ICs sind im Prinzip Kopien von Bild 1, wenn auch die zusätzlichen externen Bauteile an den AGND-Pin des IC sowie seinen NC- und seinen SYNC-Pin angeschlossen werden. Der EN-Pin wird zur Aktivierung des IC permanent mit 0 V verbunden. Ebenso kann an ihn eine Pegelumsetzer-Schaltung als Schnittstelle zu einem Logiksignal angeschlossen werden. Die Regelschleife lässt sich genau so gestalten wie für den TPS61170. Wird zur Versorgung empfindlicher analoger Verbraucher ein sehr rauscharmer Ausgang benötigt, kann der negative Ausgang des negativen Gleichspannungswandlers einem LDO für negative Spannungen zugeführt werden. Für niedrigere Spannungen bewährt sich der TPS723 (200 mA bei Eingangsspannungen von -2,7 bis -10 V), während bei höheren Spannungen der TPS7A30 (200 mA / Eingangsspannung -3 bis -36 V) und der TPS7A33 (1 A / -3 bis -36 V) am besten geeignet sind.