Wenn Sie einen USB-Stick öffnen, werden Sie mit größter Wahrscheinlichkeit folgende Komponenten darin vorfinden: Neben dem oder den Flash-Chips, die die größte Fläche einnehmen, sitzt der Controller-Chip mit USB- und Flash-Interface sowie die Spannungsversorgung. In höherwertigen Speichermedien, beispielsweise einer SSD mit SATA- oder PCIe-Interface, kommt meist noch ein RAM hinzu, das den Transfer besonders beim Schreiben von Daten in den Flash-Speicher beschleunigt.

Für den Einsatz in rauen Umgebungen ist diese Konfiguration jedoch schlecht geeignet: Schocks und Vibrationen belasten die Mechanik, zudem beanspruchen Kontakte und Temperaturwechsel im industriellen Maßstab die Lötstellen stark. Mit einer Single-Chip-Lösung, die alle Komponenten in einem IC-Gehäuse vereint und hermetisch versiegelt, lassen sich diese Problemstellen umgehen. Das BGA-Gehäuse kann wie üblich gemeinsam mit den anderen Schaltungskomponenten auf der Leiterplatte verlötet werden.

Wirkungsweise von Flash

Die Wirkungsweise der Flash-Technologie basiert auf einer elektrischen Ladung, die zwischen zwei isolierenden Schichten eingeschlossen ist. Beim Beschreiben und Löschen des Speichers werden diese Schichten durch eine erhöhte Spannung kurzzeitig leitfähig, sodass sie von der Ladung durchdrungen werden können. Da dieser Prozess die Isolationsschicht beansprucht, nimmt der Isolationswiderstand im Laufe der Zeit ab und die Zelle altert. Entsprechend geben die Hersteller in ihren Datenblättern sogenannte P/E-Zyklen an, das heißt wie häufig sich die Zelle programmieren (P) und löschen (Erase, E) lässt. Bei Flash können übrigens keine einzelnen Zellen gelöscht werden, sondern immer nur ein ganzer Block – entsprechend geht das Ändern eines einzigen Bits stets mit einem P/E-Zyklus für den ganzen Block einher.

Abstufungen beim Auslesen

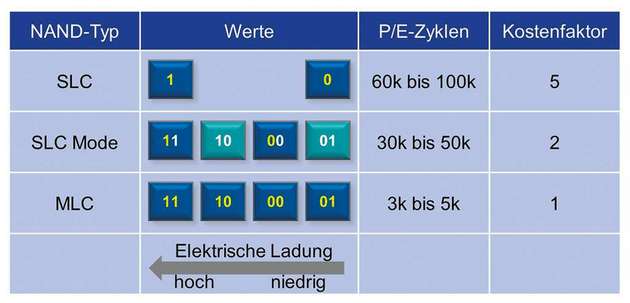

Beim Auslesen wird von der Höhe der Ladung auf einen digitalen Wert geschlossen. Bei der Single-Level-Cell (SLC) entscheidet ein Komparator, ob der gemessene Spannungswert kleiner oder größer als eine definierte Schwelle ist – entsprechend gibt er dann eine 0 oder eine 1 zurück. Bei der Multi-Level-Cell (MLC) ist die Abstufung feiner, so dass vier unterschiedliche Spannungspegel als der Zustand zweier Bits (00, 01, 10, 11) interpretiert werden können. Mit fortschreitender Halbleitertechnologie haben sich die Isolation und damit die Ladungshaltung stetig verbessert: Triple-Level-Cells (TLC) enthalten etwa acht verschiedene Spannungswerte, die als drei Bits pro Zelle interpretierbar sind. Mit der Quad-Level-Cell (QLC) ist derzeit der technologische Höhepunkt erreicht.

Mit der immer höheren Integration durch immer kleinere Strukturen verringern sich zwar die Kosten pro Bit, jedoch nehmen die Haltbarkeit und die Übertragungsrate des Speichers ab. Da die meisten Hersteller von NAND-Flash-Speichern der Nachfrage nach höherer Kapazität folgen, sind SLC-Speicher zu moderaten Preisen kaum noch erhältlich. Ein guter Kompromiss zwischen Kapazität, Anzahl der Schreibzyklen und Betriebskosten ist der Betrieb von MLC-Zellen im sogenannten SLC-Mode, auch Pseudo-SLC genannt. Dabei wird die MLC-Speicherzelle mit nur zwei statt der möglichen vier Werte beschrieben. Im SLC-Mode geht zwar nutzbare Kapazität verloren, dafür steigen aber die Zuverlässigkeit und die Langlebigkeit. Bei ungefähr doppelten Kosten im Vergleich zum MLC-Betrieb verzehnfacht sich die Anzahl der Schreibzyklen. Die nicht-sequentielle Abfolge der binären Zustände beim SLC-Mode hängt mit der erhöhten Störfestigkeit aufgrund der größeren Hamming-Distanz zusammen. Das Verfahren setzt eine enge Zusammenarbeit zwischen Controller- und NAND-Hersteller voraus, da der interne Aufbau des Flash-Bausteins eine wichtige Rolle spielt.

Flash-Controller

In der Praxis werden Flash-Bausteine nicht direkt mit einer Host-CPU verbunden. Vielmehr wird zwischen den Host und den Speicher ein Controller geschaltet, der zur Host-Seite ein Standardinterface anbietet und die Speicher mit Hilfe einer speziellen Firmware kontrolliert. Im Folgenden soll der Begriff SSD für alle Speichermedien gelten, bei denen die Flash-Chips über einen Controller unabhängig von der Schnittstelle an ein Host-System angeschlossen werden. Bei einer SSD übernimmt der Controller viele wichtige Funktionen, um dem Speicher-Subsystem ein langes Leben und hohe Geschwindigkeiten bei höchster Zuverlässigkeit zu ermöglichen. Eine dieser Funktionen ist das Wear Levelling, mit dessen Hilfe die Schreibvorgänge auf den gesamten Speicher verteilt werden, um die Lebensdauer des Systems zu maximieren. Auch das Management defekter Blöcke ist eine wichtige Aufgabe des Controllers. Eine weitere Funktion ist die Ansteuerung und Verwaltung des Caches, um die Zugriffsgeschwindigkeit besonders beim Schreiben zu erhöhen. In schnellen Systemen ist dieser Cache mehrstufig angelegt.

Optimierte Firmware

Werden alle Flash-Komponenten in ein einziges Gehäuse gepackt, so lässt sich die Firmware des Controllers bezüglich der Eigenschaften des Speichers optimieren. Dabei wird die Performance der Hardware – Zugriffsgeschwindigkeit, Datenintegrität und Haltbarkeit – fein abgestimmt. Für eine kostengünstige Lösung wird TLC-Speicher eingesetzt. Teile des TLC-Speichers werden im SLC-Mode angesteuert – als Cache für den langsameren TLC-Speicher und um die Datensicherheit für den Programmspeicher zu verbessern. Zudem sorgt die kompakte Bauform für eine gute thermische Kopplung und eine Unempfindlichkeit gegenüber Umwelteinflüssen wie Schock oder Vibration. Ein weiterer Vorteil ist die Vielfalt an Produkten, die bei gleichem Gehäuse in unterschiedlichen Speichergrößen, mit oder ohne RAM-Cache und für verschiedene Temperaturbereiche zur Verfügung stehen.

Für die Evaluierung von SSDs auf einem Chip eignet sich ein m.2-Board, das einfach eingesteckt werden kann. Aufgrund ihrer kompakten Bauweise eignet sich diese Lösung besonders für tragbare Messgeräte und Datenlogger, für Geräte in der Labor- und Medizintechnik sowie für alle Baugruppen, die Vibrationen oder Schocks ausgesetzt sind. Da der Speicher aufgelötet und nicht gesteckt ist, besteht kein Manipulationsrisiko durch Auswechseln des Datenträgers.

3D-NAND-Technologie

Eine weitere Entwicklungsrichtung bei Flash-Speichern firmiert unter dem Begriff 3D NAND. Bei dieser relativ neuen Technologie werden mehrere Speicher-Chips übereinander platziert, was zu einer hohen dreidimensionalen Packungsdichte im Chip-Gehäuse führt. Dadurch lassen sich je nach Aufbau und Betriebsart des Speichers unterschiedlich hohe Netto-Kapazitäten auf kleinstem Raum erzielen.

Anhand von zwei Beispielen soll in der Folge gezeigt werden, welchem Zweck all diese technologischen Weiterentwicklungen im Speicher-Chip-Umfeld dienen könnten. Das erste Beispiel dreht sich um Nutzfahrzeuge. Dort wird der Fahrer/Bediener heute verstärkt von Videokameras unterstützt, die Bereiche teils dreidimensional visualisieren, die aus der Position des Bedieners nicht einsehbar sind – zum Beispiel beim Rückwärtsfahren, direkt an der Baggerschaufel oder an der Hecköffnung des Fahrzeugs.

Zu Dokumentationszwecken kann das Kamerasignal direkt in einen digitalen Videorecorder eingespeist werden. Dabei muss das Speichermedium eine konstante Mindestdatenrate garantieren, damit keine Frames verloren gehen. Zudem muss es eine ausreichend hohe Anzahl von Schreibzyklen gewährleisten, um die Lebensdauer des Fahrzeugs im besten Fall zu übertreffen. Da konventionelle SD-Karten nur ein bis zwei Jahre durchhalten, ergeben sich hier wichtige Anwendungsfelder für hochintegrierte Flash-Speicher.

Automatisierte Medikamentenausgabe

Ein anderes Anwendungsbeispiel betrifft die Lagerhaltung in großen Apotheken, zum Beispiel in Krankenhäusern. Hier werden Medikamente in riesigen Mengen umgesetzt. Moderne automatisierte Systeme helfen dabei, Bestellungen zu disponieren, die Fehlerrate bei der Ausgabe zu senken, den Lagerbestand zu verwalten und dabei nie die Verfallsdaten der Medikamente aus den Augen zu verlieren. Eine Schlüsselfunktion übernehmen dabei Kameras, die jede eingelagerte beziehungsweise abgerufene Medikamentenverpackung scannen und identifizieren. Die von mehreren Seiten aufgenommenen hochauflösenden Bilder werden in einem Speicher abgelegt, per OCR oder Code dem Datensatz des betreffenden Medikaments zugeordnet und entsprechend verbucht. Da die Bilder in einer sehr raschen Abfolge eingehen, muss die dabei eingesetzte SSD eine hohe Datentransferrate haben und eine große Anzahl von Schreibzyklen ermöglichen.

QLC auf dem Vormarsch

Zusammenfassend lässt sich festhalten, dass der Integrationsgrad von Flash-basierten Speichermedien in der nächsten Zeit weiter steigen wird. Während die Versorgung mit NAND-Flash niedriger Integration (SLC, MLC) bereits stark zurückgegangen ist, hat die TLC-Technologie durch die Inbetriebnahme neuer Fertigungslinien an Fahrt aufgenommen und wird in absehbarer Zeit den größten Teil des Marktes übernehmen. Zudem erscheint am Horizont die neue QLC-Technologie. Dadurch und bedingt durch immer kleinere Halbleiterstrukturen wird die Kapazität pro Flash-Chip weiter zunehmen, gleichzeitig wird die Zahl der möglichen P/E-Zyklen aus demselben Grund abnehmen. Die Integrationsdichte, gemessen in Gigabit pro Chip, steigt. Gleichzeitig sinkt der Preis pro Bit. Entsprechend werden die Kosten pro Chip annähernd gleich bleiben.