Wie stellen Sie sich die Zukunft der Mikroelektronik vor? Welche wichtigen Trends werden Ihrer Meinung nach die kommenden Jahre prägen?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Tatsache ist, dass wir in Europa nicht die Logik- und die Memory-Bausteine mit den feinsten Strukturbreiten innerhalb der Halbleiter (Nodes) produzieren werden, selbst wenn große Hersteller wie Intel oder TSMC sich hier ansiedeln wollen. Auf diesem Gebiet sind bekanntlich nur einige wenige große internationale Hersteller tätig, die den Maschinenpark und Aufwand betreiben können, um Nodes kleiner als 5 nm herzustellen.

Welche Anwendungsbereiche treiben die 2,5D-/ 3D-Hetero-Integration maßgeblich voran?

Es sind genau die Schlagwörter, die seit 3 bis 5 Jahren in der Fachwelt zu hören sind. Die Nachfrage nach Hochleistungsanwendungen im Zusammenhang mit Rechenzentren, High Performance Computing (HPC), Quantencomputing und neuromorphem Rechnen, Smart Sensing, Optoelektronik, 5G- und 6G-Kommunikation, Künstlicher Intelligenz (KI) und auch dem Autonomen Fahren steigt stetig an.

Wenn die Leiterbahnen zukünftig noch enger, die Via-Durchmesser noch kleiner und die Wafer-Dicken noch dünner werden – wann erreichen wir die Grenze des physikalisch Möglichen?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Im Zusammenhang mit dem Mooreschen Gesetz hieß es vor einigen Jahren, dass mit den feinen inneren Strukturen langsam Schluss sein wird. Einige führende Hersteller haben angekündigt, in Zukunft auf Nodes von kleiner 5 nm zu setzen. Vor einigen Jahren konnte sich das noch niemand vorstellen.

Vor einigen Wochen haben die Forschungsfabrik Mikroelektronik Deutschland (FMD) und Intel gemeinsam mit Schlüsselakteuren der deutschen Industrie eine Roadmap 2030+ für die Forschung im Bereich der 3D-Integration vorgestellt. Welchen Beitrag wird das Fraunhofer IZM dafür leisten?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Einerseits hat unser Institut eine wichtige Rolle bei der Gesprächsanbahnung mit Intel gespielt. Wir arbeiten seit vielen Jahren eng zusammen. Der jetzt vorgestellte Forschungsfahrplan wurde in einer Reihe von Workshops erarbeitet, die von der FMD und Intel Europe Research organisiert wurden. Der erste Workshop fand bei uns in Berlin am Fraunhofer IZM statt.

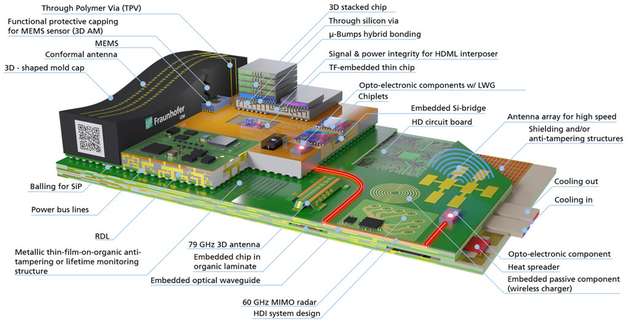

Auf der aktuellen Institutsbroschüre ist eine Visualisierung eines High-End Performance Packages (HEPP) abgebildet. Was hat es mit dieser Abbildung auf sich und was genau macht ein HEPP aus?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Die Grafik visualisiert, wie verrückt die Systeme werden, wenn sie hochfunktional sein sollen und welche Technologien dafür notwendig sind. Wir zeigen fiktiv auf, was heute bereits alles beim High-End Performance Packaging gemacht wird und wo unser Institut auf dem Gebiet der Hetero-Integration aktiv ist. Wir bringen Chips auf und in die Leiterplatte.

Im Zusammenhang mit Advanced Packaging ist immer häufiger vom Hybrid-Bonding und der Chiplet-Integration zu lesen. Auf der anderen Seite müssen beim Packaging von modernen Leistungshalbleitern wie Siliziumkarbid (SiC) oder Galliumnitrid (GaN) neue Wege beschritten werden. Wie ist das Fraunhofer IZM hierzu aufgestellt?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Wie bereits erläutert, fokussiert sich die Mikroelektronikindustrie seit einigen Jahren verstärkt auf die heterogene Integration, um mehr Rechen-, Speicher- und andere Funktionen auf einer bestimmten Fläche zu integrieren. Um die 3D-Verbindungsdichte zu erhöhen, werden mehrere fortschrittliche und/oder ausgereifte Chips in einem einzigen Gehäuse untergebracht.

Welche Ideen und Pläne gibt es für die zukünftige Gestaltung der drei Standorte des Fraunhofer IZM in Berlin, Dresden und Cottbus?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Seit 2019 wird der Innovationscampus für Elektronik und Mikrosensorik Cottbus –iCampμs Cottbus - unter Beteiligung von sechs außeruniversitären Forschungseinrichtungen sowie Professoren der BTU Cottbus-Senftenberg etabliert. Unser Institut ist an verschiedenen Projekten im Bereich Hochfrequenz- und Highspeed-Systeme und Antennenkonfigurationen beteiligt. Ein Beispielprojekt ist die Entwicklung eines mobilen Ultra-Low Power Radarsystems für Medizinanwendungen. Ich freue mich sehr, dass wir seit Anfang 2023 auch mit einer Professur im Bereich der Hochfrequenztechnik am iCampμs Cottbus vertreten sind.

Das Fraunhofer IZM trägt neben dem Begriff der Mikrointegration den Begriff Zuverlässigkeit im Namen. An welcher Stelle sollten Zuverlässigkeitsbewertungen idealerweise ansetzen?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Die Zuverlässigkeit von Elektronik ist die Basis für funktionierende Systeme. Am Fraunhofer IZM betrachten wir das High-End Performance Packaging also die Heterosystemintegration von den Materialien, Komponenten und Maschinen über die Aufbau- und Verbindungstechnologien sowie Test, Charakterisierung und Zuverlässigkeit bis zur Anwendung als Ganzes. Wir sind daher besonders stark in der Physics-of-Failure-Analysis. Das heißt wenn wir neue Systeme mit neuen Materialien und feineren Strukturen bauen, dann wissen wir je nachdem in welches Anwendungsgebiet diese fließt, welche Beanspruchungen zu erwarten sind.

Nach all den Einblicken hat man das Gefühl, es herrschen goldene Zeit für die Mikroelektronik. Ist dem tatsächlich so oder gibt es auch Herausforderungen?

Prof. Dr.-Ing. Martin Schneider-Ramelow

Die Notwendigkeit, die Maschinenparks stetig zu erneuern, und die Reinrauminfrastruktur vorzuhalten und zu betreiben, sind kostenintensiv. Hinzu kommt der Fachkräftemangel. Am Berliner Standort haben wir aktuell über 100 Labore auf einer Gesamtfläche von 8.000 m2.