Es gibt mehrere Schritte, die dabei helfen, zielgerichtet das Herzstück einer elektrischen Baugruppe – die Leiterplatte – zu gestalten. Fünf Schritte lohnen sich besonders hervorgehoben zu werden, da sie den größten Unterschied zu vergangenen Methoden bei der Entwicklung von gedruckten Schaltungen darstellen. Diese Schritte werden im Folgenden genauer beschrieben.

1. Lagenaufbau

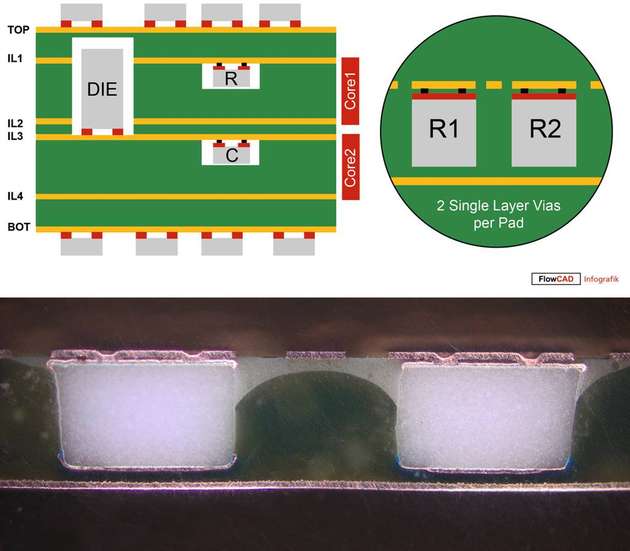

Mit dem richtigen Lagenaufbau steht und fällt der Erfolg des Designs. Der Lagenaufbau beschreibt, aus welchen Materialien die einzelnen Schichten einer Multilayer-Leiterplatte aufgebaut sind.

Die Lagen bestehen aus Kupferfolien und FR-4 Isolationsmaterial jeweils mit einer unterschiedlichen Höhe und elektrischen Eigenschaften. Sollen beispielsweise Kabelverbindungen zwischen zwei Platinen ersetzt werden, so kann dies über starr-flexible Leiterplatten erfolgen, bei denen die flexiblen Bereiche die Kabel ersetzen.

Bauteile lassen sich als Embedded Components in die Leiterplatte vergraben, und so wird der Platzbedarf reduziert und die Zuverlässigkeit gesteigert. Über die Oberflächenbeschaffenheit der Kupferlagen und die Abstände zwischen den einzelnen Lagen lassen sich Impedanzen für High-Speed-Datenübertragung einstellen und für Hochstromanwendungen kann Kupfer in größeren Dicken in der Leiterplatte verlegt werden.

All diese Aspekte können nicht losgelöst voneinander betrachtet werden. Nicht alle Materialien sind miteinander kombinierbar und nicht jeder Leiterplattenhersteller hat alle Materialien auf Lager. Hier empfiehlt sich vor Beginn des Projekts ein technologischer Austausch mit dem Leiterplattenhersteller, der die Platine später fertigt.

Auch bei besonderen Anforderungen oder hohen Stückzahlen lohnt sich ein Gespräch direkt mit dem Leiterplattenhersteller über Optimierungspotenzial bei der Materialauswahl oder Nutzenaufteilung. Es können Lagenaufbauten für die technischen Anforderungen hinsichtlich Kosten und Fertigungstechnologien optimiert werden.

Für Kleinserien und mittlere Ansprüche gibt es von Leiterplattenherstellern wie Würth Elektronik auf deren Webseiten kostenfrei etliche Vorlagen (Stackup-Templates) für einen Lagenaufbau aus Standardmaterialien zum Download, beispielsweise für das OrCAD-Datenformat. In diesen Templates sind die Materialeigenschaften und Schichthöhen bereits spezifiziert, und die Standardisierung reduziert die technischen Rückfragen und ermöglicht kurze Lieferzeiten.

Wenn die Leiterplatten für Impedanzen ausgelegt werden, nutzen Leiterplattenhersteller häufig Messgeräte von Polar Instruments, um die Platinen später zu testen. Die Lagenaufbauten werden mit den dazugehörigen Leiterbahnbreiten mit einer Software von Polar berechnet, die auch nicht öffentliche, anlagenspezifische Parameter, wie beispielsweise Unterätzung, berücksichtigt. Über das neutrale Austauschformat IPC-2581 können Leiterplattenhersteller dem Designer die Vorgaben für das Layout elektronisch übermitteln, sodass die Regeln mit Materialeigenschaften einfach in das PCB-Layout-Tool eingelesen werden können.

2. Bibliothek

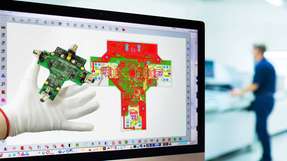

Früher wurde eine Bibliothek von Symbolen und Footprints angelegt, um die Schaltpläne und Kupferstrukturen für wiederkehrende Bauteile schneller zu zeichnen. Heute sollten diese geometrischen Elemente auch mit einem 3D-Modell des Bauteils und den Metadaten in einer Datenbank miteinander verknüpft sein. Mit 3D-Informationen können moderne Layout-Tools eine 3D-Ansicht erzeugen und mögliche Kollisionen mit Gehäuseteilen oder anderen Leiterplatten bereits virtuell erkannt werden.

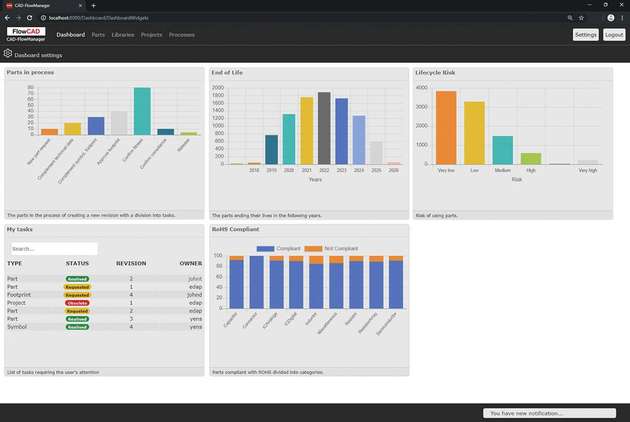

Über diese Datenbank kann der Entwickler schnell seine Bauteile für die Schaltung selektieren und dabei nach Parametern filtern, wie zum Beispiel elektrischen Eigenschaften, Kosten, Lagerbestand, Freigaben (UL, RoHS, REACH) und potenziellen Risiken für eine Bauteilabkündigung oder verlängerte Lieferzeiten und Allokation.

Bauteildatenbanken sind heute bereits häufig mit den kaufmännischen Warenwirtschaftssystemen, aber auch mit externen Informationsplattformen verknüpft. So können die Änderungsmitteilungen (PCN, Product Change Notification), die Bauteilhersteller bei jeder Änderung veröffentlichen, elektronisch ausgewertet werden. Gravierende Änderungen führen dann zu einer neuen Sachnummer für das Bauteil.

Über die Stücklisten kann auch zugeordnet werden, welches Bibliotheksbauteil in welchem Produkt verbaut wurde und wo es zu einer Rückrufaktion oder zu einem Redesign kommen muss. Über die verschiedenen Workflows lassen sich neue Bauteile, Freigabeprozesse und Änderungen auf mehrere Personen kontrolliert verteilen und mit ERP, PLM oder einer Warenwirtschaftssoftware integrieren.

3. Schaltplan erfassen und kritische Bereiche simulieren

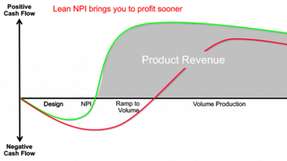

Der Zeitaufwand und die Kosten, einen Prototyp zu erstellen und mit bemusterten Bauteilen zu messen, erfordern auch hier geänderte Entwicklungsmethoden. So wie im mechanischen Design komplexe Crashtests von Automobilen virtuell simuliert werden können, ist es möglich, Teilaspekte der elektrischen Baugruppe bereits im Entwicklungsstadium zu simulieren. Analoge Schaltungselemente und parasitäre Eigenschaften wie Induktivitäten, Kopplungen und Kapazitäten lassen sich mit der Software PSpice simulieren.

Der Sonderfall der Datenübertragung von Signalen mit sehr steilen Flanken stellt hohe Ansprüche an die Signalintegrität. Durch Modelle oder Extraktionen des Layouts lassen sich Impedanzsprünge und Übersprechen sehr genau simulieren. Hier kommen spezielle Solver zum Einsatz, die für die Schnittstellen wie PCI Express oder DDR4-Speicher alle Parameter berücksichtigen, die in einer Compliance-Messung erforderlich sind.

Niedrigere Versorgungsspannungen ermöglichen eine längere Batterielebensdauer, machen aber die Stabilität von Stromversorgungen auf der Leiterplatte sehr schwierig. Mit einem Power Tree können alle Elemente in einem Versorgungssystem bereits im Stromlaufplan erfasst und die Leistung für Zweige des Systems richtig dimensioniert werden. Sobald das Layout erstellt wird, lassen sich physikalische Eigenschaften und die Platzierung von Verbrauchern und Abblockkondensatoren in einer Power-Integritätssimulation analysieren und optimieren.

In der Simulation können sowohl die Wechselwirkung der Stromdichte und Eigenerwärmung bis zum eingeschwungenen Zustand, aber auch unterschiedliche Umgebungstemperaturen und maximal zulässige Temperaturen innerhalb von Bauteilen berücksichtigt werden. Designs, die robust für Signalintegrität und Power-Integrität ausgelegt wurden, sind auch deutlich weniger anfällig für elektromagnetische Störungen. Durch die virtuelle Kontrolle und Optimierung kommt es zu weniger Versuchen im EMV-Labor und zu weniger Redesigns.

4. Constraint Manager

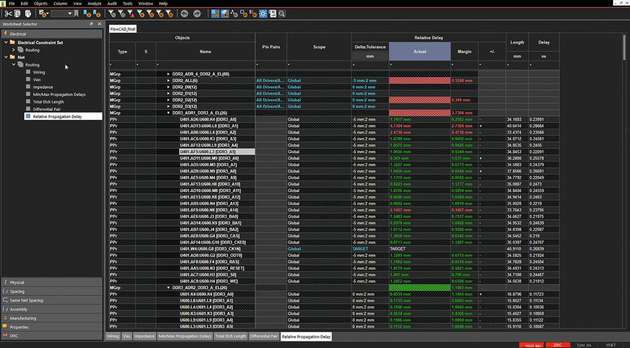

Die Zahl der zu beachtenden Designregeln steigt kontinuierlich in rasantem Tempo. Leiterplattendesigns mit tausenden zu beachtenden Regeln sind heute keine Seltenheit und können ohne Softwareunterstützung nicht mehr effizient umgesetzt werden.

Moderne Layout-Systeme verfügen über einen Constraint Manager mit integriertem Design Rule Check. Designregeln lassen sich den Elementen einer Baugruppe, wie Bauteile, Verbindungsnetze oder Kupferflächen, zuweisen. Wichtig ist hier die Granularität des Constraint-Managers, um gezielt Spezialfälle und Ausnahmen von generellen Regeln zu spezifizieren und beim Design-Review zu verifizieren.

Darüber hinaus können komplexe Regelsätze, zum Beispiel für eine DDR3-Speichertopologie, in der Bibliothek gespeichert werden. Wenn eine solche Topologie verwendet werden soll, kann der Regelsatz mit hunderten von Details zugewiesen werden, und es werden alle Regeln wie Impedanzen, minimale und maximale Leitungslängen, die Anzahl von Durchkontaktierungen oder die maximale Anzahl von Lagenwechseln zugeordnet.

Durch die Zuordnung weiß der PCB Editor von den Regeln und kann diese während des Routens mit dem Layout abgleichen. Verstößt der Designer gegen eine Regel, wird er durch eine Fehlermarkierung ähnlich der Rechtschreibkorrektur in der Textverarbeitung in Echtzeit auf den Verstoß hingewiesen. Der Designer kann sofort reagieren und den Fehler beheben, oder erst seinen Gedanken zu Ende routen und im Anschluss die Fehler gezielt abarbeiten.

5. DFM Checks, Bestücker und Testverfahren

Früher war es üblich, dass ein PCB Layout als Gerber Filme ausgegeben und anschließend beim Leiterplattenhersteller in der CAM-Abteilung die Daten auf Fertigbarkeit geprüft wurden. Womöglich hat der Leiterplattenhersteller das Design dann geringfügig verändert, damit er es ätzen konnte. Das war soweit in Ordnung, wie es nur um Aufbau und Verbindungstechnik ging. Bei miniaturisierten oder Impedanz kontrollierten Baugruppen sind die Toleranzen bereits vom Layouter ausgeschöpft, sodass in der CAM-Abteilung ohne Kenntnis der Funktion das Layout nicht mehr geändert werden darf.

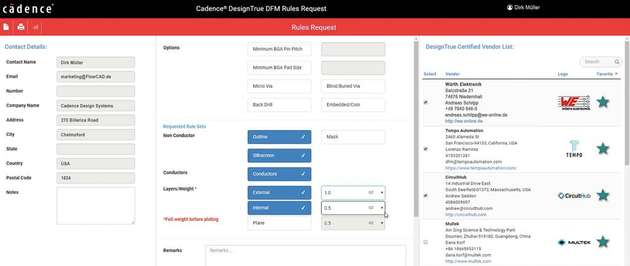

Um kostspielige und zeitaufwendige Iterationen zu vermeiden sind heute CAM-Checks im OrCAD und Allegro PCB Editor möglich. Über ein kostenfreies DFM-Portal von Cadence können Leiterplattendesigner bei Herstellern die maschinenspezifischen DFM-Regeln abhängig von ihren Anforderungen erfragen.

Die Leiterplattenhersteller haben in ihrer Ansicht des Portals die Möglichkeit, die Maschinenparameter einzugeben und einen elektronischen Regelsatz als Technologiefile für den PCB Editor zu exportieren. Als Antwort bekommt der Layouter einen DFM-Regelsatz, der in den PCB Editor importiert werden kann.

Jetzt können ähnlich dem Constraint Manager auch die Regeln für die Fertigung, wie etwa minimaler Abstand von Bauteilen zur Board-Kontur, in Echtzeit beim Layouten geprüft werden. Durch das Einlesen eines zweiten Regelsatzes kann sichergestellt werden, dass diese Leiterplatte auch bei einem zweiten Lieferanten als Second Source gefertigt werden kann.

Die Entwicklung von Leiterplatten ist im Wandel von der Entflechtung von bedrahteten Schaltungen zu hochkomplexen, gedruckten Schaltungen. Durch die Miniaturisierung, Leistungssteigerung und höhere Übertragungsraten spielen die parasitären Effekte eine immer größere Rolle. Die Leiterplatte wandelt sich vom Verbindungsträger zu einem elektrischen Bauteil mit geplanter Kapazität, Impedanz und HF-Strukturen als IoT-Antenne.