Die Entwicklung einer Hardware-Emulationsplattform ist ein umfangreiches Projekt. Die zahlreichen komplexen Eigenschaften des DUT (Device Under Test), die zu berücksichtigen sind, reichen von einigen Millionen ASIC-Gatteräquivalenten bis zu weit über zehn Milliarden Gatter.

Eine DUT-Topologie kann von vielen Tausenden oder Millionen komplexen Taktverteilern angetrieben werden, die von zahlreichen asynchronen Primärtaktgeneratoren gespeist werden. Die Plattform sollte große Mengen komplexer Speicher und IP-Blöcke (Intellectual Property, IP) bereitstellen und zudem umfassende E/A-Verbindungen bieten.

In der weiteren Entwicklung umfasst der Prozess die Gestaltung von Leiterplatten mit mehrfach programmierbaren Bauelementen, die das DUT abbilden sollen, sowie eingebettete DUT-Speicher, DUT-Debug-Speicher zur Erfassung der DUT-Aktivität während der Laufzeit und Hilfskomponenten. Auch umfasst das Verfahren die Gestaltung von Racks für Leiterplatten und von Schränken, in denen die Racks untergebracht werden.

Kühlsysteme mit geringem Stromverbrauch

Leistungsstarke Netzteile und Kühlsysteme vervollständigen die Aufgabe zur Gestaltung der Hardware. Je nach Emulatorart können die Kühlsysteme entweder auf Ventilator-unterstützter oder natürlicher Luftumwälzung beruhen.

Für eine bessere Skalierbarkeit und zur Erhöhung der Kapazität auf mehrere Milliarden Gatter sind mehrere miteinander verbundene Schränke erforderlich. Das angestrebte Ziel besteht darin, einen einteiligen Schrank mit der größtmöglichen Kapazität zu errichten, um die erforderliche Zahl der Schränke zu reduzieren und die maximale Kapazität zu erreichen.

Besonders wichtig ist das hierarchische Netzwerk, das mehrfach programmierbare Geräte miteinander verbindet und sich von der Leiterplatte bis hin zu Racks und Schränken erstreckt. Das Netzwerk sollte Routing-Ressourcen besitzen, um unterschiedliche Designs mit hoher Ausführungsgeschwindigkeit zu emulieren.

Ein übergeordnetes Entwicklungsziel erfordert eine Beschränkung des Stromverbrauchs auf ein Minimum, um die Betriebskosten zu minimieren und eine hohe Zuverlässigkeit zu gewährleisten. Daher werden bei der Berechnung der Energiemenge für das Lüftungs- und Kühlsystem die Abmessungen und das Gewicht der Emulationsplattform berücksichtigt. Außerdem wird bei der Erschaffung eines Hardware-Emulators ein zukunftsorientiertes Hardware-Design angestrebt.

Design mehrfach programmierbarer Geräte

Anbieter von Emulationsplattformen können heute eine von drei verschiedenen Technologien nutzen. Bei zwei werden speziell angefertigte Chips (Prozessoren oder EOC (Emulator on Chip)) verwendet, bei der dritten serienmäßig angefertigte Chips (FPGAs), die von Xilinx geliefert werden.

Die ersten zwei Architekturen wurden in den letzten zwanzig Jahren von mehreren Gerätegenerationen geprüft, sodass für die absehbare Zukunft neue Generationen von Chips entwickelt werden können. Die Entwicklung von Silizium für fortgeschrittene Technologien ist jedoch zeitaufwendig und teuer und erfordert hochqualifizierte Fähigkeiten sowie außergewöhnliches Talent. In der Vergangenheit erforderte die Entwicklung von Emulationssystemen für speziell angefertigte chipbasierte Systeme etwa vier bis fünf Jahre.

Entwicklung des DUT Compilers

Der erste Schritt beim Einsatz einer Emulationsplattform besteht darin, das DUT über den Compilierungsprozess auf die mehrfach programmierbaren Ressourcen des Emulators abzubilden. Während ein Team für die Entwicklung des Hardware-Anteils eines Emulators zehn bis zwanzig Entwickler und wahrscheinlich ebenso viele Halbleiter-Entwickler benötigen kann, kann die Entwicklung des Compilers bis zu 100 Software-Experten binden. Der Compiler des Emulators beansprucht den größten Teil des Personalbudgets der F&E-Abteilung.

Der Compiler des Emulators nutzt verschiedene Compilierungs-Technologien, vor allem bei der FPGA-basierten und bei der EOC-basierten und weniger bei der prozessorbasierten Plattform. Zu den Aufgaben der Compilierung gehören für Erstere die Synthese auf Register-Transfer-Level (RTL), die Partitionierung der Netzliste, die Timing-Analyse, die Anordnung der Taktsignale (Clock mapping), die Speicherzuordnung, das Board-Routing sowie die Platzierung und das Routing (P&R) von FPGA oder EOC. Beim prozessorbasierten Emulator werden die Platzierung und das Routing des programmierbaren Chips durch die Verteilung der Berechnungen auf boolesche Prozessoren ersetzt.

Am Anfang wird die DUT-Beschreibung durch eine Kombination von Verilog, VHDL oder SystemVerilog HDL analysiert. Der RTL-Code wird in eine strukturelle Netzliste überführt. Da das Ziel der RTL-Kompilierung für einen Emulator rein funktional ist, können für eine schnellere Compilierung verschiedene für die Optimierung der physischen Implementation wichtige Aspekte der Synthese weggelassen werden. Zudem kann die Tiefe der Netzliste noch optimiert werden, um ein endgültiges Compilierungsergebnis mit den besten Kapazitäts- und Leistungsmerkmalen zu erzielen.

Die Anbieter von Emulationssystemen nutzen in der Regel speziell angefertigte Synthesetechnologien mit diesen Eigenschaften. Nach der Erstellung der DUT-Netzliste divergiert der Compilierungsverlauf je nach Emulationstechnologie.

Bei FPGA- und EOC-basierten Plattformen wird die Gatternetzliste auf ein Array aus mehrfach programmierbaren Bausteinen aufgeteilt, die das DUT implementieren. Bei der Aufteilung der Netzliste kann ein nicht perfekter Partitionierer einem oder mehreren programmierbaren Bausteinen Logikblöcke ungleichmäßig zuweisen, was trotz der Nutzung von schnellen Datenübertragungsraten im Emulatornetz zu einer Überlastung der Verbindung führen kann.

Ebenso kann ein Partitionierer, der mit der Taktung nicht umgehen kann, lange kritische Pfade erzeugen, indem er sie durch mehrere Chips, sogenannte Hops, leitet, was die Geschwindigkeit der Emulation beeinträchtigt. Ein präzises Timing-Analysewerkzeug kann solche langen Pfade erkennen und Hops vermeiden. Eine noch größere Herausforderung besteht in einer effizienten Anordnung der zahlreichen Taktsignale. Zudem kann eine intelligente Clock-Gating-Strategien da Abhilfe schaffen.

Nach all diesen Schritten müssen die mehrfach programmierbaren Chips platziert und geroutet werden. Das P&T-Tool (Werkzeug für Platzierung und Routing) wird entweder vom Anbieter des serienmäßigen FPGA bereitgestellt oder vom Anbieter des EOC entwickelt.

Beim prozessorbasierten Emulator dagegen teilt der Compiler das DUT unter den Prozessoren auf und plant einzelne boolesche Operationen in Zeitabschnitten ein. Der Compiler muss sich nicht mit Platzierung und Routing befassen und weist stattdessen bestimmten booleschen Prozessoren Berechnungen zu.

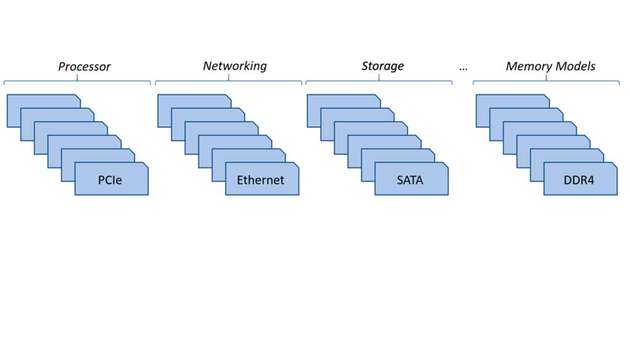

Die Implementierung von Speichern des DUTs erfolgt in allen Emulationssystemen über Speichermodelle, die die On-Device-Speicherressourcen und On-Board-Standard-Speicherchips so konfigurieren, dass sie als ASIC-Speicher verschiedener Formen sowie als andere spezialisierte Speicherbausteine wie DDR3-SDRAM, GDDR5 und SDRAM fungieren.

Die Kompilierung eines Designs ist ein rechenintensives Verfahren, das von der Größe und von der Komplexität des Entwurfs abhängt. Um das Verfahren zu beschleunigen, wird der Prozess in mehrere Teilprozesse (Threads), die im Rechenzentrum gleichzeitig laufen können, stark parallelisiert.

Diese Parallelisierung fügt der ohnehin schon komplexen Aufgabe, einen Compiler zu entwerfen, eine weitere Dimension hinzu. Der Compiler eines Emulators benötigt moderne Technologien für Synthese, Partitionierung, Timing-Analyse, Clock-Mapping, Plazierung und Routing, die zudem noch stark parallelisiert werden müssen. Es ist nicht verwunderlich, dass das F&E-Team ihm so viel Aufmerksamkeit schenkt.

Entwurf des Laufzeitbetriebssystems

Nachdem das DUT auf der Emulationsplattform abgebildet wurde, kann es ausgewertet und mithilfe von Laufzeitsoftware oder dem Betriebssystem des Emulators getestet werden. Die Laufzeitsoftware umfasst zwei verschiedene Bestandteile.

Die Aufgabe des ersten besteht darin, das DUT auszuwerten, wobei das Betriebssystem und die Software in einem oder mehreren Host-Computersystemen laufen und eine umfangreiche Firmware in den Emulator geladen wird. Sie verwalten die Ein- und Ausgabevorgänge des in der Plattform abgebildeten DUT und bieten den Benutzern die Möglichkeit, alle typischen Laufzeitaufgaben zu starten, zu stoppen, zum Anfang zurück zu gehen, eine Schleife zu bilden, Einzelschritte auszuführen, zu speichern und wieder herzustellen.

Im Gegensatz zu den Vorläufern können die heutigen Emulatoren in mehreren Betriebsarten eingesetzt werden. Neben dem ICE-Modus beherrschen sie auch den Beschleunigungsmodus, der sich weiter in zwei Unterklassen unterteilen lässt: zyklusbasierte Beschleunigung, die wegen der begrenzten Beschleunigung im Vergleich zu einem HDL-Simulator nicht beliebt ist, und transaktionsbasierte Beschleunigung.

Der ungetaktete Transaktionsmodus führte zur Nutzung des Emulators in einer virtuellen Umgebung und zur Möglichkeit, Software auf einer virtuellen Plattform auszuführen. Zudem befasst sich die Laufzeitsoftware mit allen Echtzeitproblemen oder Virtualisierungsschichten, die erforderlich sein könnten, um die Hardware- und Verarbeitungselemente für jene Anwendungen bereitzustellen, die für den Systembenutzer sichtbar sind.

Der zweite Baustein von Laufzeitsoftware ist der DUT-Debugger. Das Debuggen in einem Emulationssystem ermöglicht die interne Sichtbarkeit und Steuerbarkeit eines DUT während der Laufzeit. Die Sichtbarkeit und Kontrollierbarkeit kann durch das Einfügen von Monitoren und Aktoren oder speziellen Instrumenten oder durch eine Kombination aus beidem in die Siliziumstruktur der mehrfach programmierbaren Elemente oder zur Kompilierzeit integriert werden.

In allen Fällen werden die Sichtbarkeit und die Steuerbarkeit vom Debugger verwaltet. Er muss deshalb alle modernen Debugging-Mittel wie SVAs, Checker, Monitore und Coverage unterstützen.

Umgebung für Verifizierung einrichten

Der Aufbau eines Ecosystems zur Unterstützung eines Emulators umfasst mehrere Aspekte, von denen einige mit dem DUT, andere mit der Testumgebung zusammenhängen. Alle DUTs, insbesondere große DUTs, enthalten umfangreiche eingebettete Speicher, die im Emulator abgebildet werden können. Die Erstellung von Speichermodellen ist zwar an sich kein großes Projekt, erfordert aber ein gewisses Maß an Fachwissen.

Wenn ein Emulator im virtuellen Modus eingesetzt wird, kann die Schnittstelle zwischen dem DUT und der virtuellen Umgebung über ein VIP modelliert werden, das ein Kommunikationsprotokoll, einen sogenannten Transaktor, implementiert. Die Eigenschaften eines Transaktors hängen von der Anwendung ab.

Transaktoren für die gängigsten Protokolle, wie PCIe, USB, Ethernet, werden von Emulations- oder Drittanbietern zur Verfügung gestellt. Ihre Schaffung erfordert Fähigkeiten im Bereich des IP-Designs und die Spezialisierung auf bestimmte vertikale Märkte wie zum Beispiel Kommunikation oder Networking. Die Benutzer von Emulatoren benötigen möglicherweise auch benutzerdefinierte Transaktoren, wenn ihre Designs proprietäre Protokolle verwenden.

Eine weitere Kategorie der Emulation-VIP umfasst Geschwindigkeitsadapter aus elektronischen Karten, die als FIFOs fungieren, wenn der Emulator im ICE-Modus eingesetzt wird. Reale Zielsysteme laufen typischerweise mit Multi-Gigahertz-Raten, die um ein Vielfaches schneller sind als die Geschwindigkeit des Emulators. Durch den Einbau von Geschwindigkeitsadaptern zwischen den Emulator-IO und dem Zielsystem wird gewährleistet, dass die zwei Taktdomänen ohne Datenverluste oder Protokollverletzungen kommunizieren.

Fazit

Um ein hochmodernes Emulationssystem zu erstellen, muss sich das Entwicklungsteam mit mindestens vier oder fünf technologischen Bereichen der Entwurfsautomatisierung befassen und aus sehr unterschiedlichen technologischen Bereichen schöpfen. Nur so kann gewährleistet werden, dass alle Elemente eines Emulators optimal zusammenarbeiten.

Ein Emulator ist nur dann wettbewerbsfähig, wenn alle Technologien einwandfrei und ohne Raum für Fehler funktionieren. Die Begrenzung der Plattform wird vom schwächsten Glied definiert.