Quantencomputer gelten als Lösung für die steigende Forderung nach mehr und mehr Rechenleistung und immer größeren Datenmengen. Um Quantenprozessoren jedoch anwendbar und skalierbar zu machen, gibt es derzeit noch verschiedene Hürden, die überwunden werden müssen. Die Fehleranfälligkeit der Quantenbits, oder kurz Qubits, gilt aktuell als eine der größten Herausforderungen in der Quantencomputer-Entwicklung.

Ziel der Partner ist es, ein System mit verschiedenen Quantenprozessoren zu entwickeln, das auf supraleitenden Schaltkreisen der nächsten Generation basiert und eine sehr geringe Fehlerrate aufweist. Damit erreichen die Qubits eine höhere Qualität. Der Ansatz gilt als weltweit führend und wird auch von Google, IBM und Intel verfolgt.

Als Gesamtmeilenstein wird am Forschungszentrum Jülich in Kürze ein erster Prototyp des QSolid-Halbzeit-Demonstrators mit zehn Qubits, integriertem Softwarestack und Cloud-Anwenderzugriff in Betrieb gehen und es ermöglichen, Anwendungen sowie Benchmarks für Industriestandards zu testen. Das Projekt wird durch das Bundesministerium für Bildung und Forschung (BMBF) mit einer Gesamtsumme von 76,3 Millionen Euro unterstützt.

Errungenschaften der CMOS-Halbleiterfertigung für künftige Quantenprozessoren

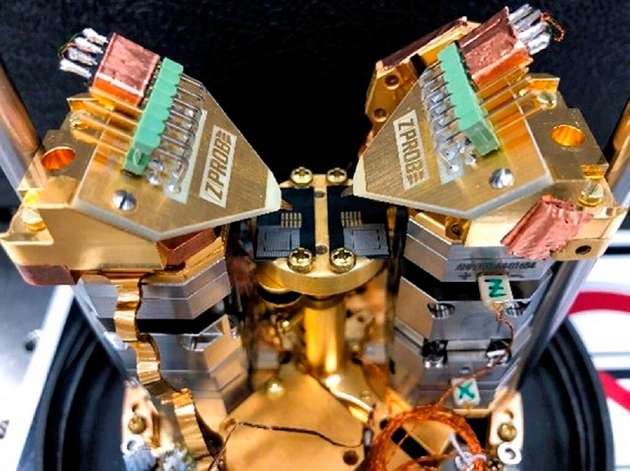

Das Fraunhofer IPMS ist Teil des Arbeitspaketes „Technology for Hardware-Intergration“. Gemeinsam mit GlobalFoundries und dem Fraunhofer IZM-ASSID wird an der Co-Integration einer CMOS-Kontrolllogik zusammen mit der Quantum-Processing-Unit (QPU) gearbeitet, um komplexe Verkabelungen und Leitungen im Quantencomputer zu verringern. Denn diese verringern die Leistungsfähigkeit des Prozessors und erschweren damit die Niedrighaltung der Temperatur – insbesondere, wenn sich die Qubit-Zahl in zukünftigen Prozessoren erhöhen wird.

Hierzu wird eine Interposer-Technologie entwickelt, die sich auf hochdichte, supraleitende Verbindungen und thermische Entkopplung durch fortschrittliches Packaging konzentriert. Die Herausforderung besteht darin, die CMOS-Chips unter kryogenen Bedingungen weiterhin nutzbar zu machen, jedoch gleichzeitig die Temperatur der Prozessoren für die Qubits niedrig zu halten. Das Center Nanelectronic Technologies (CNT) nutzt dabei seine Expertise und Infrastruktur in der hochmodernen, industriekompatiblen CMOS-Halbleiterfertigung im 300-mm-Waferstandard. Dies betrifft zum Beispiel Herstellungsprozesse wie die Abscheidung und Nanostrukturierung im Wafermaßstab oder auch die kryo-elektrische Charakterisierung.

„Gemeinsam mit unseren Partnern in Dresden konnten wir das Design für die Co-Integration von CMOS- und Quantenchips sowie geeignete Materialen für das Temperaturmanagement festlegen. Eine darauf basierende erste Generation Interposer wurde hergestellt und bei kryogenen Bedingungen erfolgreich getestet. Dies umfasst auch den Nachweis der supraleitenden Eigenschaften der verwendeten Materialien wie etwa der Indium-basierten Bumps. Außerdem waren die Tests für die kryogene Charakterisierung der CMOS-Chips von GlobalFoundries erfolgreich“, verkündet Marcus Wislicenus, Gruppenleiter für Quantum Technologies am Fraunhofer IPMS.

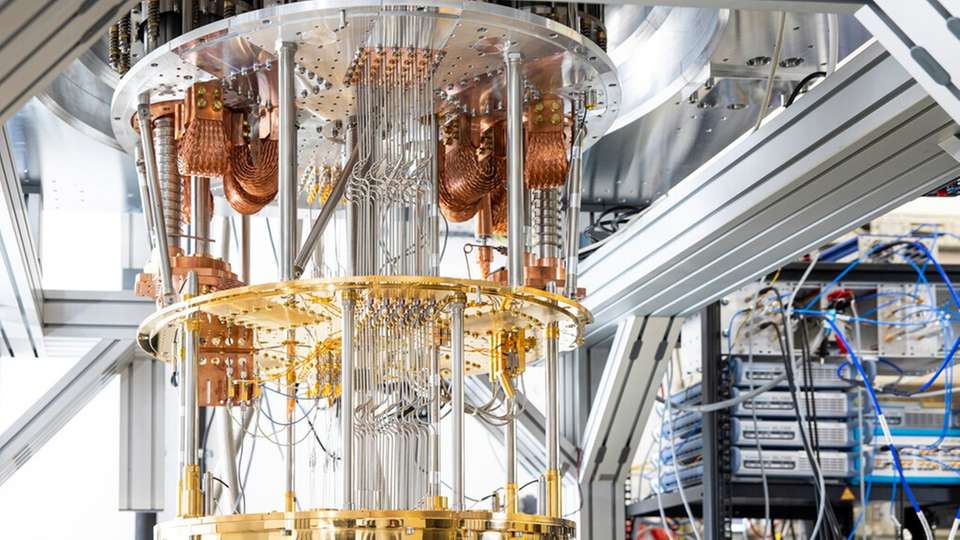

Eine gemeinsam nutzbare Quantencomputer-Infrastruktur am Forschungszentrum Jülich

Der 10-Qubit-Prototyp ist nur ein erster Zwischenschritt hin zu einer höheren Skalierung. Zum Projektende im Dezember 2026 soll das System so weiterentwickelt werden, dass es bestenfalls 30 Qubits bei größtmöglicher Fehlerkorrektur kontrollieren kann. „Die letzten zweieinhalb Jahre haben wir ausgezeichnete Kapazitäten und ein System mit vielversprechenden Leistungswerten auf den Weg gebracht. Während wir noch letzte Teilsysteme integrieren und aussteuern, arbeiten wir parallel bereits an der Erhöhung der Leistungsfähigkeit des Prototyps, der komplexe Rechenoperationen für Anwendungen in der Industrie und Wissenschaft bewältigen soll“, so Projektkoordinator Prof. Frank Wilhelm-Mauch.

Um das ehrgeizige Ziel eines unabhängigen, in Deutschland hergestellten Quantencomputers zu erreichen, bringt QSolid 25 Forschungseinrichtungen, Unternehmen und Start-ups aus ganz Deutschland zusammen. Gemeinsam wollen die Projektpartner den Weg zur Kommerzialisierung ebnen und einen Demonstrator entwickeln, der externen Nutzern über die „Jülich UNified Infrastructure for Quantum computing“ (JUNIQ) zugänglich gemacht und auf ihre individuellen Bedürfnisse zugeschnitten werden soll.