Um die neuesten Energieeffizienzstandards für Netzteile zu erfüllen, muss man auf einen hohen Wirkungsgrad achten. Eine wichtige Rolle dabei spielt die Climate Savers Computing Initiative (CSCI). Sie ist Partner des Energy-Star-Programms und will Hersteller davon zu überzeugen, die Effizienz bei der Stromversorgung von Rechnern zu verbessern und den Energieverbrauch des Rechners im Standby- oder Ruhezustand zu verringern. Sie bewertet Produkte nach den Klassen: Basis, Bronze, Silber, Gold und nun auch nach der neusten Spezifikation: Platin. Sie bezieht sich auf Einphasen-Netzteile mit AC-Eingang im Leistungsbereich von 500 W bis 1 kW, gemessen bei 230 VAC Eingangsspannung. Auch der Leistungsfaktor wird als Funktion der Last definiert. Im Folgenden geht es darum, wie sich ein digital geregeltes 720-W-AC/DC-Netzteil entwickeln lässt, das alle CSCI-Platinum-Spezifikationen erfüllt.

Eingesetzte Hardware

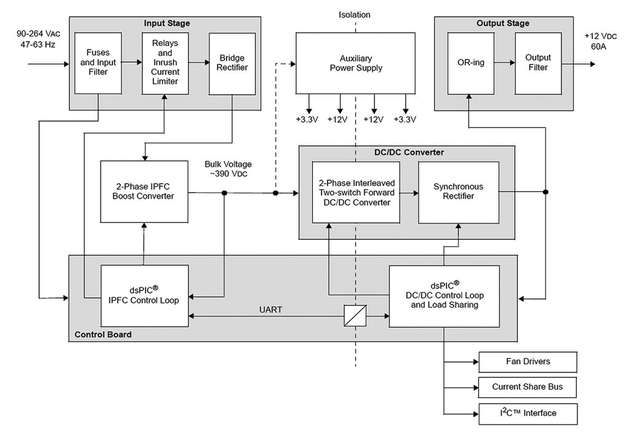

Verschachtelte Topologien bieten Vorteile, wenn ein hoher Wirkungsgrad sowie eine hohe Zuverlässigkeit und Leistungsdichte gefordert sind. Die Aufteilung jeder Topologie in zwei parallele Phasen und die Verschachtelung des Betriebs mit 180°-Phasenverschiebung verringert den Brummstrom. Die verringerten Spitze-zu-Spitze-Stromwerte in diesen Topologien führen zu niedrigeren Betriebstemperaturen, was geringeren Verlusten entspricht. Da jede Phase nur die Hälfte des Gesamtstroms führen muss, verringern sich die Leitungsverluste in Kondensatoren, im Kupfer der Leiterplatte und in den magnetischen Bauteilen um das Vierfache, da der Stromwert im Quadrat in Gleichungen zur Verlustberechnung eingeht. Ein weiterer Vorteil verschachtelter Topologien ist der halbierte Nennstrom jeder Phase. Damit verringert sich die Größe von Drosseln, Transformatoren, PCB-Leiterbahnen, MOSFETs, Kühlkörpern und Dioden. Im Referenzdesign in Abbildung 1 sind die Leistungsfaktorkorrektur(PFC)-Verstärkerstufe und der 2-Switch-Durchflusswandler in einer verschachtelten 2-Phasen-Architektur dargestellt. Die ersten Bauteile am Netzanschluss sind eine Filterdrossel und ein paralleler 1-μF-Kondensator, um elektromagnetische Störungen zu unterdrücken. Der Drossel folgen zwei Sicherungen, für die Phase und den Neutralleiter. Ein paralleler 470-V-Varistor schützt vor Überspannungsspitzen. Die Eingangsfilterstufe verwendet zwei weitere Filter, die aus einer Gleichtaktdrossel, zwei mit Masse verbundener Y-Kondensatoren und einem parallelen Entstörkondensator (X-Kondensator) mit metallisierter Polypropylenfolie bestehen. Ein NTC-Widerstand mit einem Nullstromwiderstand von 10 Ω bei 25 °C begrenzt den Einschaltstrom auf unter 40 A. Dieser NTC wird über ein Relais umgangen, sobald sich die Hauptspannung stabilisiert hat und der Controller das System hochfährt. Die Eingangsspannung liegt an einem Brückengleichrichter mit einer Nennspannung von 1,3 kV und einem Nennstrom von 43 A an. Über dem Ausgang dieses Gleichrichters befinden sich ein weiterer Varistor und ein Entstörkondensator, um vor Transienten zu schützen.

Der verschachtelte PFC-Wandler (Interleaved PFC) verwendet zwei identische Aufwärts-/Boost-Wandler, die parallel gekoppelt und 180° phasenverschoben sind. Ein AC/DC-Wandler ist die IPFC-Stufe. Er wandelt die Eingangswechselspannung in einen geregelten High-Voltage-DC-Ausgang um. Die PFC-Stufe formt den Spulenstrom ähnlich zur gleichgerichteten Wechselspannung, um einen hohen Leistungsfaktor und geringen Klirrfaktor beizubehalten. Diese Stufe arbeitet im Continuous-Conduction-Modus, um den Oberwellengehalt des Eingangsstroms zu verringern. Die Boost-PFC-Topologie erfordert die Ansteuerung von nur einem Low-Side-MOSFET. Der 2-Kanal-MOSFET-Treiber MCP14E4 von Microchip bietet CMOS-Push-Pull-Ausgänge, die als Quelle und Senke 3,5 A bei 12 V bereitstellen. Dieser steuert beide Phasen. Zwei Stromsensoren (CT; Current Sense Transformer) mit einem Windungsverhältnis von 50:1 erfassen den Strom. Sie befinden sich auf der Drain-Seite des Low-Side-MOSFETs anstatt auf der Source-Seite, um eine bessere Rückkopplung mit verringertem Schaltrauschen zu erzielen. Der Stromausgang wird über einen 15-Ω-Widerstand in ein Spannungssignal umgewandelt. Ein Serien-Parallel-Netzwerk aus vier Widerständen (zwei 15-Ω-Widerstände in Serie, zwei parallel) wird für CT verwendet – für verringerte Toleranzen des Shunts und höhere Genauigkeit. Die Reihenschaltung halbiert auch die Spannung für die Komparatoreingänge des dsPIC Digital Signal

Controllers.

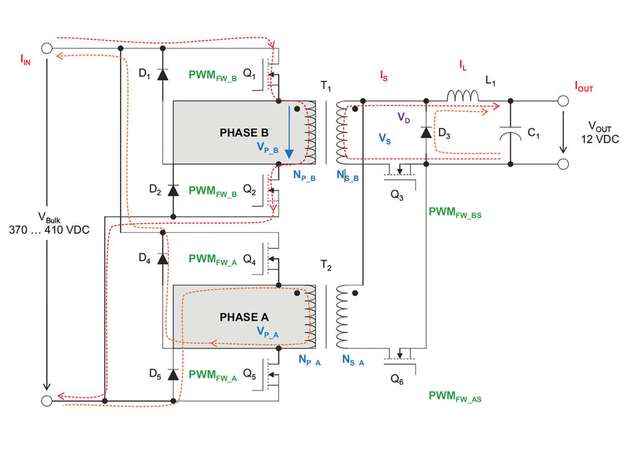

Der verwendete MOSFET ist ein 600-V-CoolMOS-C6-Leistungstransistor von Infineon. Die gewählte IPFC-Diode ist der Z-Rec-Gleichrichter, eine Siliziumkarbid(SiC)-Schottky-Diode von Cree. Die Sperrverzögerungsverluste machen einen erheblichen Teil der Boost-Wandler-Verluste aus. Diese Verluste werden durch SiC-Dioden verringert, da mit ihnen fast keine Sperrverzögerungszeit auftritt. Im Gegensatz zu einer Sperrwandler-Topologie verwenden Durchflusswandler Spannungstransformatoren, um während der Einschaltzeit des MOSFETs Energie an den Ausgang zu übertragen. In einem 2-Switch-Durchflusswandler wird über die High-Side- und Low-Side-MOSFETs Spannung über die Primärwicklung angelegt. Beide werden gleichzeitig ein- und ausgeschaltet. Sobald Spannung an der Primärwicklung anliegt, werden alle Wicklungen positiv. Wird der MOSFET Q3 eingeschaltet, baut sich der Strom in der Sekundärwicklung auf.

Da Strom immer noch durch L1 und C1, die Last und über den Rückkanal durch D3 fließen kann, baut sich dieser auf, bis sein Wert den Strom durch D3 erreicht und übersteigt. An diesem Punkt stoppt der Durchlassstrom durch D3 und die Spannung VS über der Sekundärspule wird zum Start von L1 verwendet. Damit werden die Drossel L1 und der Ausgangskondensator C1 geladen und Leistung wird am Ausgang bereitgestellt. Werden die MOSFETs Q1 und Q2 abgeschaltet, kehren sich die Spannungen an allen Wicklungen um. Der Sperreffekt sorgt dann für eine hohe Spannung über der Primärwicklung des Transformators. Die Spitzen werden durch die parallelen Dioden D1 und D2 gekappt. Die Dioden leiten die im Magnetfeld gespeicherte Energie zurück in die Versorgungsleitungen. Da der Lade- und Entladeprozess ungefähr die gleiche Zeitdauer in Anspruch nehmen, darf das Tastverhältnis 50 Prozent nicht überschreiten, da dies zu einer treppenförmigen Sättigung des Transformatorkerns führt. Kehrt sich die Spannung auf der Sekundärseite um, wird der MOSFET Q3 abgeschaltet und die Drossel L1 sorgt für eine weitere Stromzufuhr in C1 und die Last. D3 wird damit in Durchlassrichtung vorgespannt.

In einer verschachtelten Architektur werden die Phasen A und B mit einer Phasenverschiebung von 180° kommutiert. Da das maximale Tastverhältnis auf 50 Prozent begrenzt ist, wird die Gesamtdauer, bei der der Ausgangsstrom durch L1, C1 und D3 gesteuert wird, sehr klein.

Obwohl auch ein Gate-Treiber-Schaltkreis mit direkter Ansteuerung der Low-Side und einem zusätzlichen Gate-Treiber-Transformator für die High-Side zum Einsatz kommen könnten, kann dies zu Zeitunterschieden zwischen beiden Schaltern führen. Damit verringert sich der Wirkungsgrad und die Belastung der Bauteile nimmt zu. Es ist einfacher, einen Gate-Treiber-Transformator mit der gleichen Windungszahl für die Sekundärwicklung zu verwenden. Um eine hohe Bandbreitenrückkopplung zu erzielen und die Leistungsfähigkeit zu erhöhen, kommt ein High-Side-Shunt-Widerstand für die Ausgangsstromrückkopplung zum Einsatz. Dieser Widerstand befindet sich zwischen dem Ausgangskondensator und dem Ausgangsfilter, um die Lastschritte so früh wie möglich zu erkennen. Um die Verluste des Shunt-Widerstands zu verringern, werden zwei parallele 500-μΩ-Widerstände eingesetzt. Eine High-

Side-Stromüberwachung mit dem Operationsverstärker MCP6H02 von Microchip sorgt für Rückkopplung. In dem Referenzdesign ersetzt ein MOSFET die Gleichrichterdiode, um den Wirkungsgrad zu erhöhen und Signalverzögerungen zu kompensieren.

Leistungsfähigkeit verbessern

Für erhöhten Wirkungsgrad wird die Schaltperiode der PFC-Stufe verändert, wenn das System in einem stabilen Zustand ist. So lassen sich die Schaltverluste verringern. Die Schaltfrequenz wird dynamisch angepasst – basierend auf den jeweiligen Lastbedingungen. Der diversen Werte für die PFC-Schaltperiode werden in einer Lookup-Tabelle gespeichert. Diese Werte werden dann auf Basis der berechneten Stromreferenz für die Stromrückkopplungsschleife verwendet. Ein Frequenzjitter-Algorithmus sorgt für leistungsfähigere EMI-Tests. Dabei wird das im System erzeugte EMI-Rauschen mittels Dreieckmodulation der Schaltfrequenz über eine Reihe von Frequenzen gespreizt. Die Ausgangsspannung der PFC-Stufe wird im stabilen Zustand verringert, um den Wirkungsgrad bei geringen Lasten zu verbessern. Dies wird direkt von der Sekundärseite aus gesteuert, indem die Laststrom-

information zurück in den Primärkreis übertragen wird.